About Project MEKOPP:

The aim of project MEKOPP is to scale-up photonic chip production by streamlining chip testing and fabrication validation methods. Photonic integrated circuit (PIC) production can be categorized into three major operations: chip fabrication, chip testing, and packaging. Chip fabrication is done in cleanrooms, where batches of wafers are processed together using the same steps. Chip testing verifies that the production steps resulted in the expected structures on the chip. The goal is to achieve a high-yield fabrication run, meaning that a high fraction of chips (or dice) are produced as expected. Packaging involves the adding of inputs, outputs, interconnections, additional chips, and housing to the fabricated dies. While the fabrication of photonic dies is easily scalable due to these wafer-scale production processes, the testing of the dies remain a largely manual operation. PICs contain waveguides, through which optical signals must be passed to test their propagation properties, and electronically triggered tuners and actuators, which must be tested to ensure the correct manipulation of the propagating signal. Each wafer typically contains several of these chips, and testing cannot begin until they are diced into individual dies and packaged with photonic inputs and outputs and electronic interconnections. 80% of chip production costs are in the packaging step, meaning that most of the production cost is paid upfront before the yield of a fabrication run is known. Moreover, current testing technologies are limited in terms of automation, the number of functions that can be tested at once (test density) and the speed at which to test these functions (test throughput). A fully packaged chip with fabrication defects which are only diagnosed at testing is a total waste in terms of materials, time, and energy.

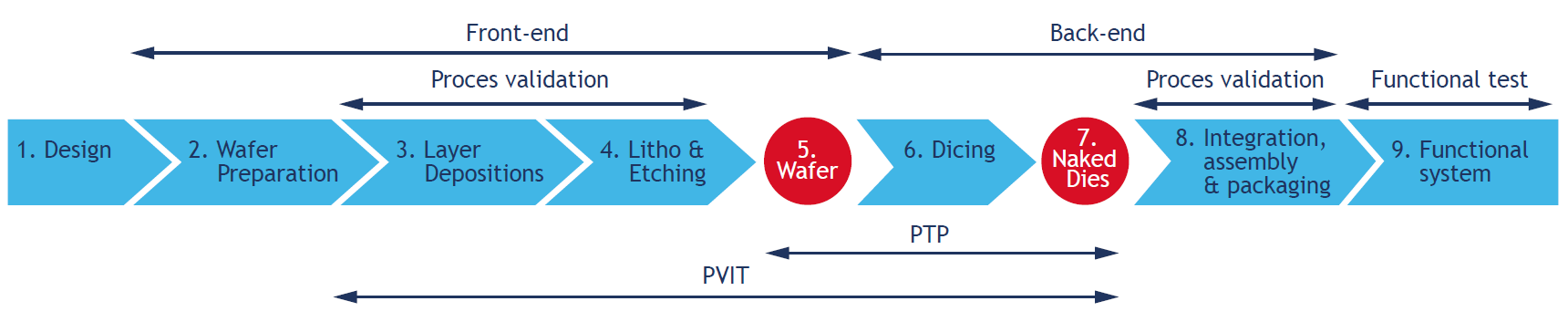

The various links of the PIC supply chain and the projected areas of effect of Project MEKOPP’s testing machines.

Project MEKOPP aims to design and prototype testing equipment which can identify defect-free ‘good’ dies in between production steps fully automatically. Two state-of-the-art test machines are proposed: a photonics visual inspection tool (PVIT) to perform visual verification of the structures on-chip (AKA lithography-check), and a photonic test prober (PTP) for measuring the photonic and electronic functionalities of the chips. Such testing methods would allow engineers to redirect packaging resources towards good dies only with minimal effort. It would also allow engineers to create spec sheets, gather statistics and thus identify which fabrication steps cause the most defects and optimise production on that basis. It is expected that such methods would halve energy consumption, material waste, and wear-and-tear of fabrication equipment.

The role of LioniX International:

As prospective end-user of the testing machines with decades of daily experience in PIC testing, LioniX International will carry out functional testing of the PTP and PVIT prototypes developed in the project and aim to integrate these in their productions line. LioniX will also consult on the test cases to identify which functions require the most improvement. Additionally, LioniX will propose system requirements of the PTP machine, drawing on its expertise in assembly and module packaging. This will verify the technology readiness level of both machines in cases that mirror their final deployment on the market. LioniX International will also supply test chips and wafers to allow other consortium members to test the devices during production and design phases.

Further information:

Our consortium partners High Tech NL, Holland Semiconductors, and Workfloor have parallel press releases about Project MEKOPP. The project is funded by the European Regional Development Fund through the OP Oost program.